Atividade #1344

FechadaDesenvolvimento da PCB modelo FF20

Descrição

Para fazer a interligação entre myRIO, Raspberry Pi, sensores, motores e bateria, deve ser desenvolvida uma placa de circuito eletrônico que será fixada dentro do peito do robô.

Repositório do Github da RoboIME: https://github.com/roboime/HRR-Hardware

Arquivos

Atualizado por Gabriel Lima há mais de 5 anos

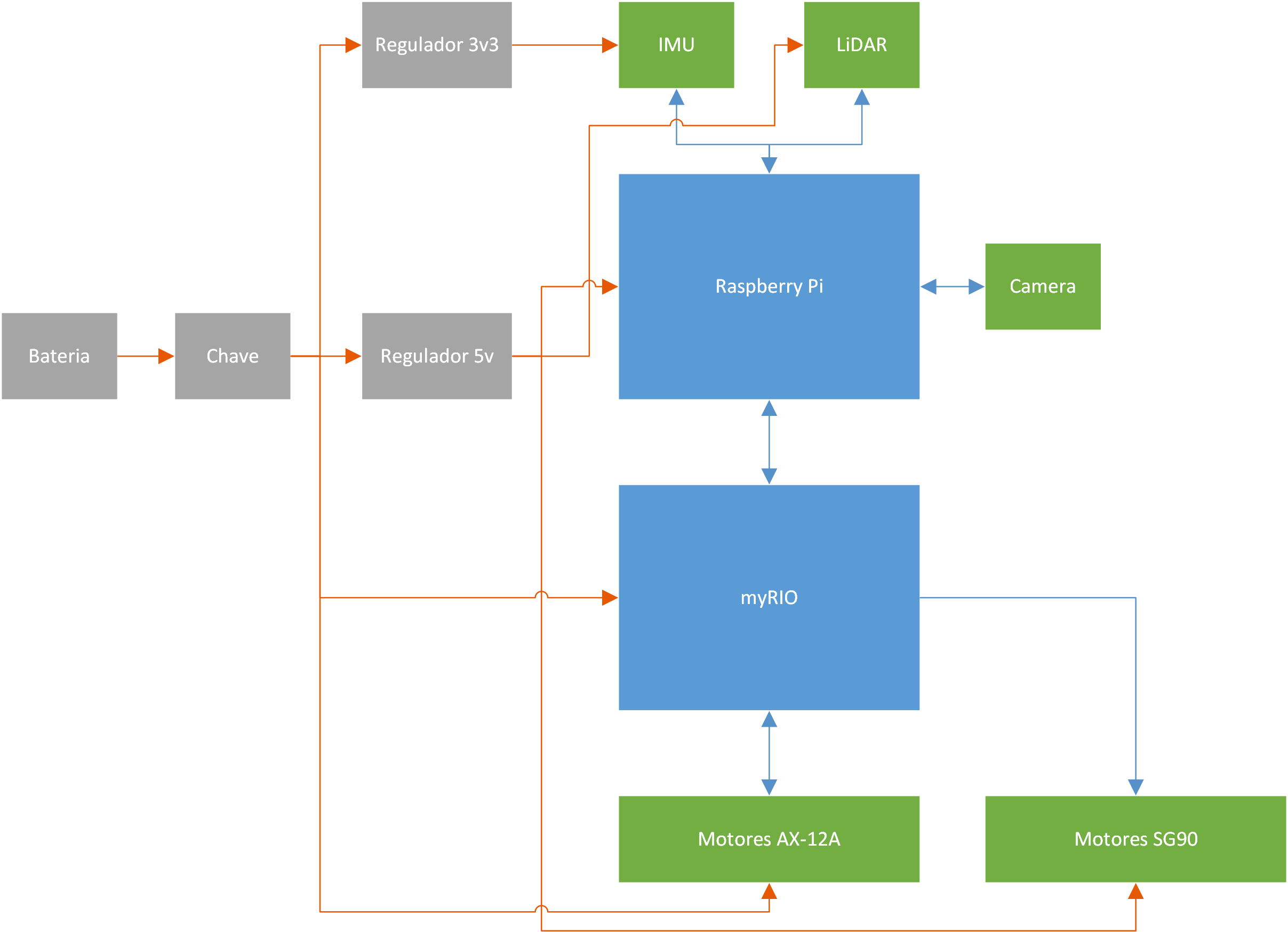

- Arquivo Diagrama_de_Blocos.png Diagrama_de_Blocos.png adicionado

Diagrama de blocos do hardware

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

- Arquivo HRR-Hardware.pdf HRR-Hardware.pdf adicionado

Dei uma olhada no esquemático e vou deixar a versão pdf em anexo.

Como ficaram as simulações dos circuitos de step down que vocês fizeram no WeBench? Conseguiu substituir alguns componentes do esquemático por alguns do partsbox?

Lembra de conferir se os footprints no .PcbDoc estão condizentes com o empacotamento que você escolheu

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Vocês incluíram as conexões do Breakout IMU e do servo motor?

Atualizado por Gabriel Lima há mais de 5 anos

Adicionei hoje os conectores dos servos 9g e do IMU.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

- Arquivo tps56339.pdf tps56339.pdf adicionado

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Conferi o esquemático do step down de 3.3V.

Do jeito que está parece que vai funcionar bem.

Vou deixar umas informações do datasheet que não são críticas, mas podem influenciar no layout:

Cin¶

If the input supply is located more than a few inches from the device or converter,

additional bulk capacitance may be required in addition to the ceramic bypass capacitor. An electrolytic capacitor

with a value of 47 uF is a typical choice.

Página 21 do datasheet em anexo

No caso, não foi adicionado o capacitor no circuito. Então o circuito fica bem próximo ao conector da bateria.

Pode-se adicionar o capacitor mencionado a cima para dar mais segurança e liberdade no design também.

Cout¶

The COUT is the sum of nominal output capacitance. Two 22-uF, 0805, 16V capacitors are

recommended for VOUT <= 5V

Página 17 do datasheet em anexo

No caso, os capacitores que vocês escolheram são de 10V. No entanto, acho que não tem muito problema manter eles porque ainda fica bem longe da tensão de saída que é 3.3V.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Esquemático step down 5V¶

Capacitor Cff1¶

É melhor trocar o capacitor Cff1. Eu vi aqui que o empacotamento dele 0201, que é muito pequeno e não tem necessidade.

Confiram os outros resistores e capacitores e vejam se tem algum que não seja 0402, 0603 ou 0805 em medidas imperiais.

Componentes fora dos empacotamentos acima podem ser usados para cumprir critérios mais específicos, mas no geral ou serão muito pequenos ou muito grandes para utilização ordinária.

PGND¶

Tem que aterrar o PGND também. Eu olhei o diagrama de blocos do CI e vi que não há pull-down interno. Na verdade, a tolerância é dele é baixa (-0.1 / 0.1).

Lembrem de adicionar stitches próximos a esse pino durante o layout.

Cin¶

Vale a pena adicionar um capacitor bulk na entrada Vin nesse caso. É o mesmo caso que o outro, mas vai ser mais difícil deixar os dois circuitos (5v e 3.3V) bem próximos da alimentação.

Lê-se bem próximo como uma distância menor que 1 polegada entre o conector da bateria e o CI em si.

If the input voltage supply is located far from the TPS566231 and TPS566238 circuit, additional input bulk capacitance is recommended, typical values are 100 uF to 470 uF.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Confiram se o pitch dos headers que vocês escolheram é 2,54mm.

Se não for, tem que substituir para que sejam porque é o tamanho padrão para os headers da raspberry e dos conectores DuPont dos jumpers.

Confirmem também se o pitch do header da MyRio também é 2,54mm. Provavelmente será, mas é bom conferir.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

- Arquivo tps566231.pdf tps566231.pdf adicionado

Atualizado por Nicolas Oliveira há mais de 5 anos

Gabriel Lima escreveu:

Diagrama de blocos do hardware

No diagrama de blocos é sempre interessante indicar qual o tipo (protocolo) de comunicação entre os blocos.

Atualizado por Nicolas Oliveira há mais de 5 anos

Melhorar os esquemáticos com mais uso das net labels, por exemplo a label GND. Em especial no componente TPS566231. Isso torna a visualização mais próxima do que é apresentado nos typical application (que é nosso objetivo).

A conferência pode ser facilitada se os valores dos componentes aparecerem no esquemático, ou se a BOM for gerado.

Melhorar a organização do esquemático, está difícil de entender quem se relaciona com quem ao meu ver.

Atualizado por Gabriel Lima há mais de 5 anos

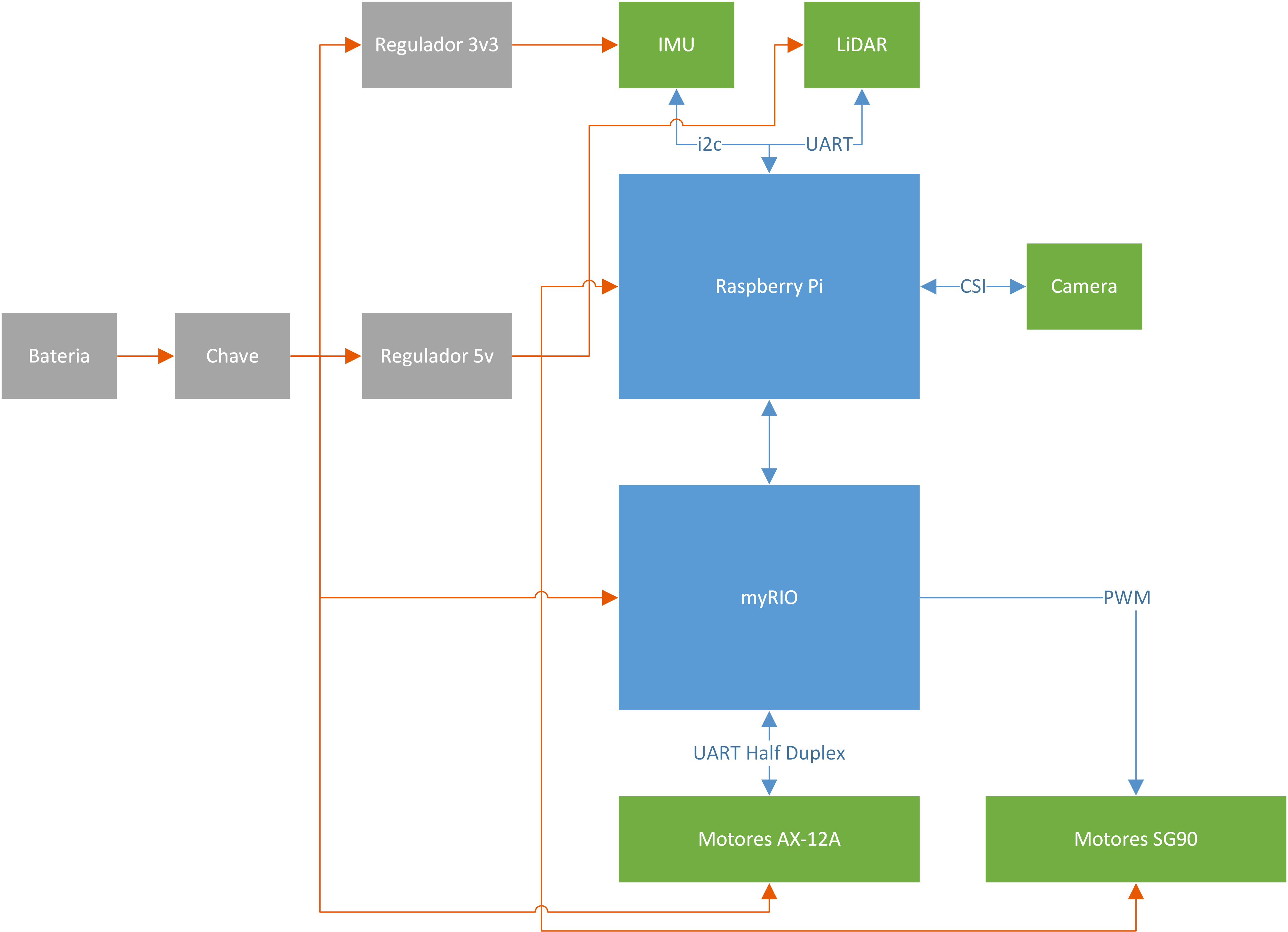

- Arquivo Diagrama_de_Blocos_r2.png Diagrama_de_Blocos_r2.png adicionado

Diagrama de blocos com os protocolos de comunicação adicionados

Atualizado por Gabriel Lima há mais de 5 anos

Fiz também todas as correções que o Erick e o Nícolas passaram. Adicionei os capacitores às entradas dos reguladores de 5v e 3v3, organizei os esquemas utilizando Net Labels e o PGND foi aterrado. Troquei também o Cff1 de 0201 por 0603. Só não entendi a parte de colocar os valores no esquemático. Seria adicionar um text string do lado de cada componente com algo do tipo "47uF 0805"?

Atualizado por Gabriel Lima há mais de 5 anos

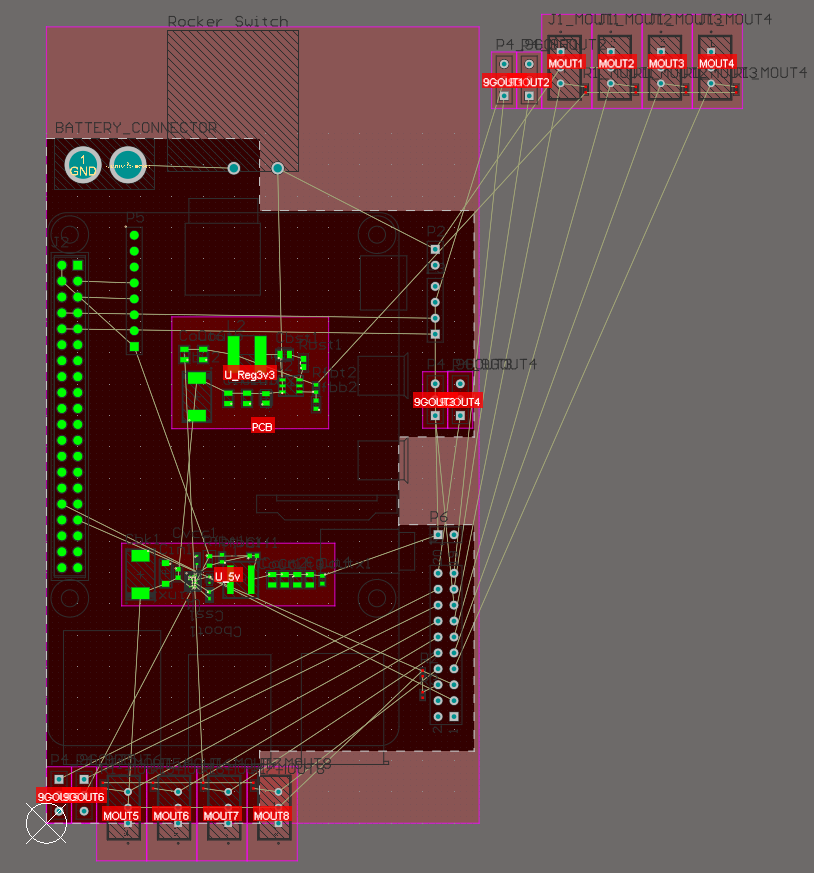

Comecei aqui a fazer o posicionamento dos componentes e percebi que o tamanho da placa vai realmente ter que aumentar em ambos os sentidos.

Atualizado por Gabriel Lima há mais de 5 anos

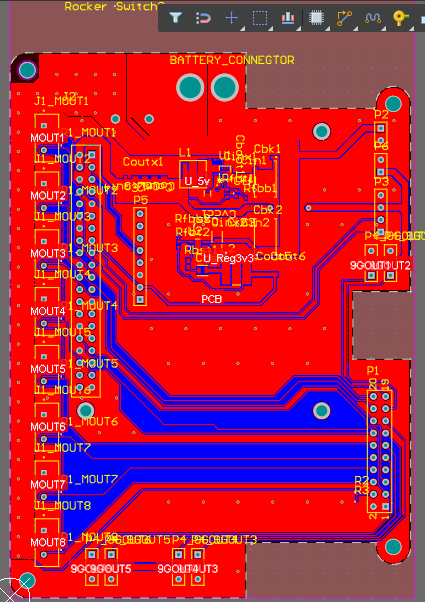

- Arquivo PCB_2020-10-07.png PCB_2020-10-07.png adicionado

Atualizado por Gabriel Lima há mais de 5 anos

Uma coisa que eu percebi enquanto estava posicionando os componentes é que o CI do regulador de 5v é bem pequeno (1.50mm x 2.00mm). Isso pode causar problemas do tipo ser impossível de soldar ou a PCB custar muito caro? Ou dá uma diferença muito pequena?

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Gabriel Lima escreveu:

Uma coisa que eu percebi enquanto estava posicionando os componentes é que o CI do regulador de 5v é bem pequeno (1.50mm x 2.00mm). Isso pode causar problemas do tipo ser impossível de soldar ou a PCB custar muito caro? Ou dá uma diferença muito pequena?

Com ferro de solda e estanho não deve dar para soldar bem. Acredito que a melhor saída seria pedir o stencil da placa quando enviar os Gerber files para manufatura e aqui usar pasta de solda com assoprador ou forno, que seria o jeito mais fácil de soldar até os maiores.

Com relação ao preço da PCB, vocês tem que ver a largura e o espaçamento entre os pads do empacotamento. Se ele for menor que 6mil (approx 0,15 mm), vai aumentar consideravelmente o preço. Essa restrição vale para qualquer componente do circuito e para as trilhas.

Atualizado por Gabriel Lima há mais de 5 anos

Medi aqui a distância entre os pads e o tamanho deles e vi que a menor delas foi de 7.685mil, então imagino que estamos dentro dos limites da manufatura.

Atualizado por Gabriel Lima há mais de 5 anos

Quais outras limitações eu devo colocar? O que seriam mínimos para larguras de trilhas, espaçamentos, tamanho da fonte no overlay, etc.?

Atualizado por Gabriel Lima há mais de 5 anos

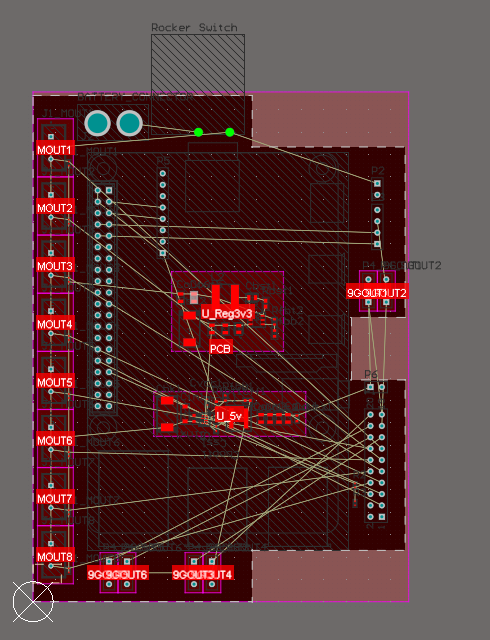

- Arquivo PCB_2020-10-08.png PCB_2020-10-08.png adicionado

Outra dúvida que eu tive foi em questão desse Rocker Switch. A princípio, eu escolhi o que a SSL está usando atualmente, mas estou com dificuldades de fazê-lo caber. Seria uma boa troca colocar o mesmo circuito de power da VSS, com um switch pequeno e um MOSFET? Eu vi que nesse caso não daria para acionar o mosfet diretamente com o VIN, visto que a nossa bateria é 3S e a tensão passaria do limite de 10V do MOSFET, teria que usar um pequeno regulador de 5V.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Gabriel Lima escreveu:

Quais outras limitações eu devo colocar? O que seriam mínimos para larguras de trilhas, espaçamentos, tamanho da fonte no overlay, etc.?

Use o PCBSaturn para calcular a largura indicada para as trilhas. O mínimo para trilhas é 6 mil, mas é bom colocar a mais quando possível. Uma largura de 10 mil deve ser o suficiente para trilhas de pinos digitais. Os espaçamentos entre trilhas e pads se chama clearence e vai ter regras separadas no menu do Altium.

O tamanho da fonte no overlay não tem muita restrição, mas é bom colocar elas em um tamanho confortável para você ler e conseguir debugar, soldar e fazer manutenção depois. Isso vai fazer diferença. Lembra de colocar manualmente nos headers também

Atualizado por Gabriel Lima há mais de 5 anos

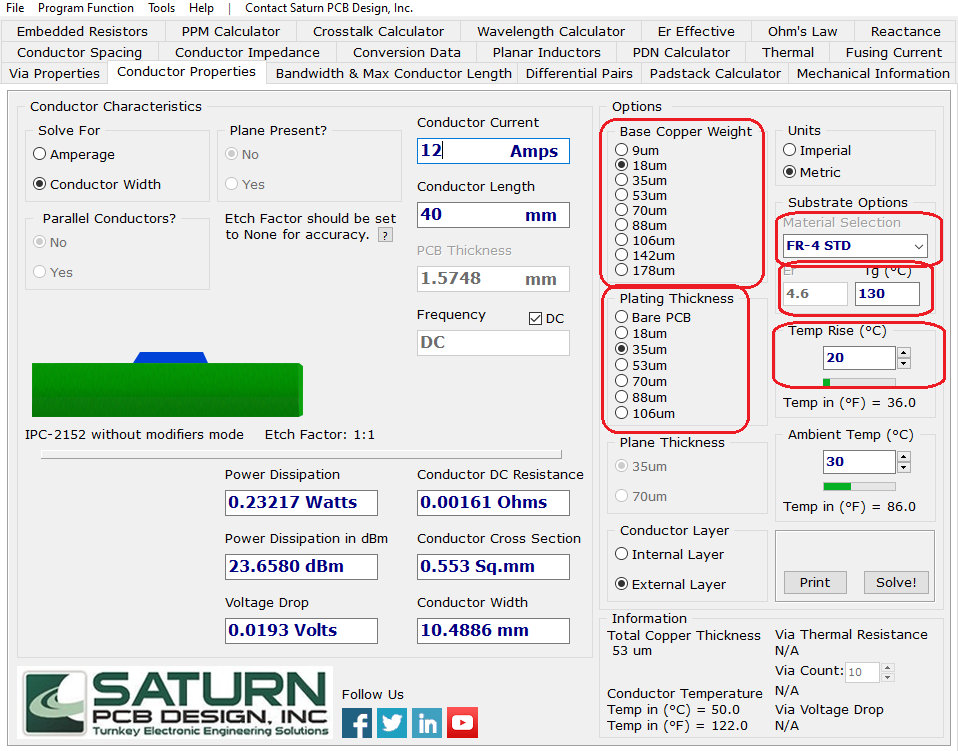

- Arquivo Saturn_PCB.png Saturn_PCB.png adicionado

O que eu devo colocar em cada um desses parâmetros circulados de vermelho?

Atualizado por Gabriel Lima há mais de 5 anos

Existe também uma distância mínima que a trilha tem que estar da borda da placa?

Atualizado por Gabriel Lima há mais de 5 anos

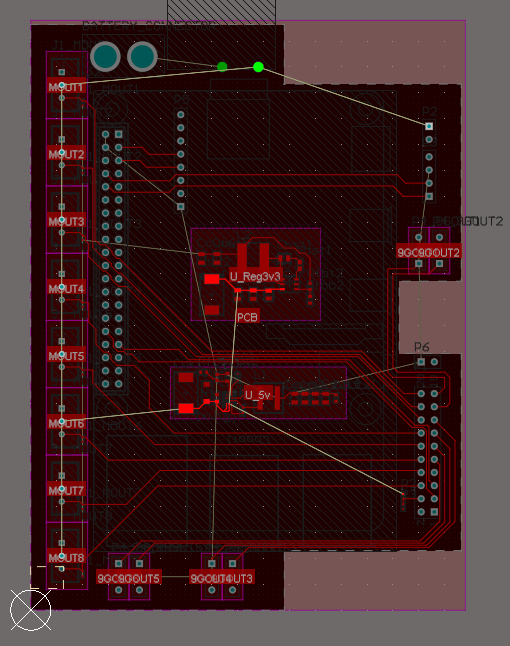

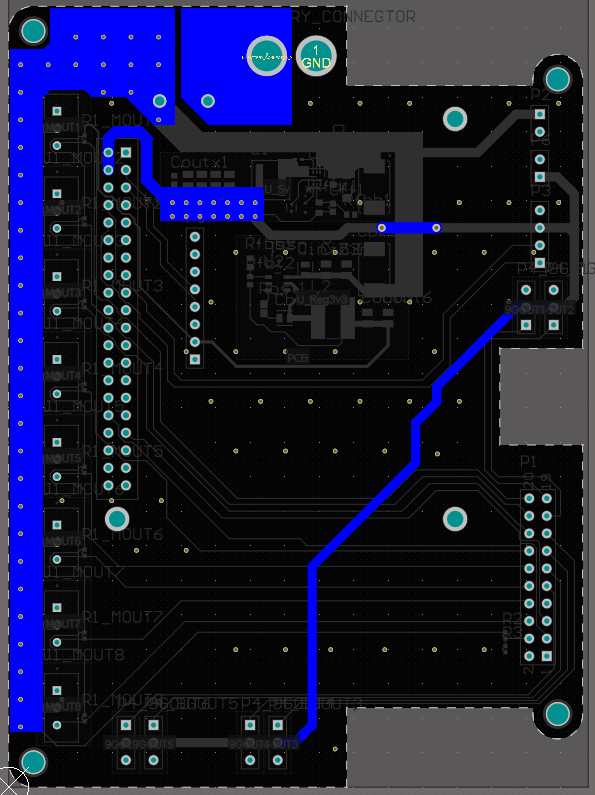

- Arquivo PCB_2020-10-09.png PCB_2020-10-09.png adicionado

Coloquei todas as trilhas já, com exceção das de alimentação.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Gabriel Lima escreveu:

O que eu devo colocar em cada um desses parâmetros circulados de vermelho?

Copper¶

Muda a unidade para imperial

Grossura do cobre:

35 um equivale a 1oz/ft^2 de cobre, que é a medida padrão.

Geralmente as emrpesas de manufatura dão só a grossura final do cobre. Não tenho certeza se elas preenchem com 1oz de cobre já da placa, com plating ou um mix dos dois.

O ideal é confirmar onde vai ser feito o pedido da placa e confirmar isso com eles, mas veja se tem muita diferença entre colocar

1oz base copper weight/Plating thickness: bare PCB ou;

0.5oz base copper weight/Plating thickness: 0.5oz

Se n fizer muita diferença, não precisa se preocupar e vc pode colocar qualquer um dos dois.

Substrato¶

Usa FR-4 STD mesmo e não mexe no Tg

Temp Rise¶

Não deve mudar tanto o resultado final. Coloca uns 40 pensando em uma temperatura final de 70, por exemplo, mas é difícil de prever. Estabelece uma faixa de valores razoável.

Lembra também que isso é uma estimativa de valor mínimo. É bom colocar uma margem de segurança em cima do valor que for dado

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Gabriel Lima escreveu:

Existe também uma distância mínima que a trilha tem que estar da borda da placa?

Existe sim, mas elas não sao muito grandes. Só cuidado para não deixar tangenciando.

Dá uma olhada na tarefa da placa da VSS que eles tiveram um problema desse na manufatura.

Atualizado por Gabriel Lima há mais de 5 anos

Temos um projeto sem erros elétricos na compilação! Todas as trilhas já estão roteadas. Fiquei com dúvida apenas no "minimum solder mask sliver". Quanto devo colocar nas regras?

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Gabriel Lima escreveu:

Temos um projeto sem erros elétricos na compilação! Todas as trilhas já estão roteadas. Fiquei com dúvida apenas no "minimum solder mask sliver". Quanto devo colocar nas regras?

Isso seria o tamanho das ilhas de solda, que vão facilitar na hora de colocar os componentes em si. A rule não costuma ser um problema, mas é interessante colocar algo que fique tranquilo de soldar depois. Geralmente as que vêm de footprints confiáveis já são os indicados.

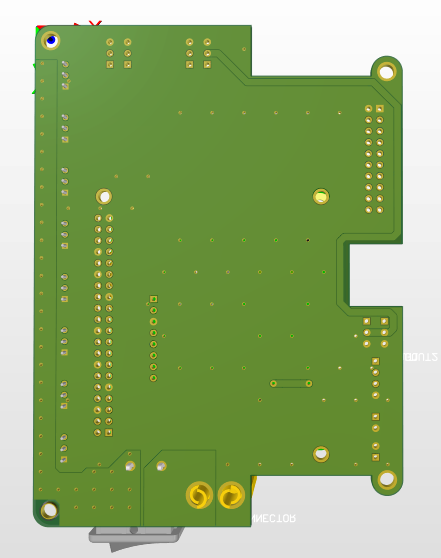

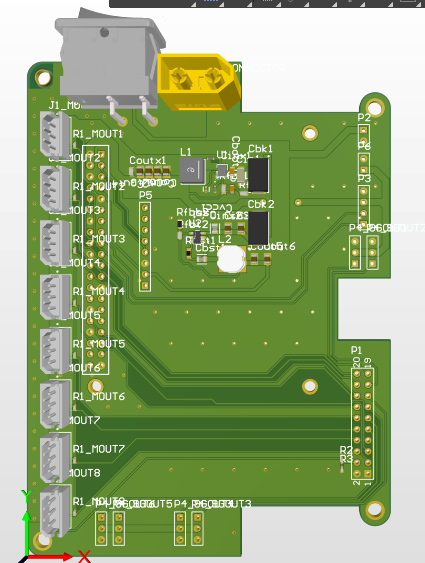

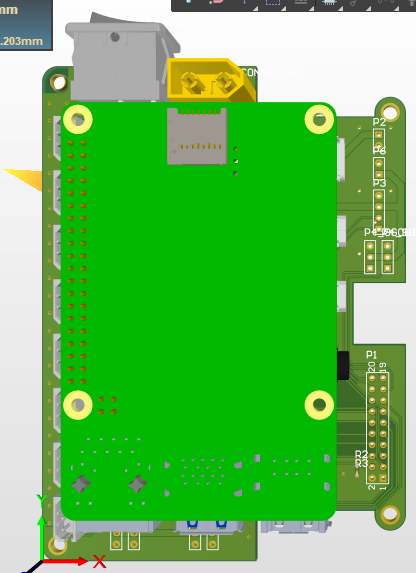

Manda a foto da Top e bottom layer em 2d e em 3d aqui

Atualizado por André Vidal há mais de 5 anos

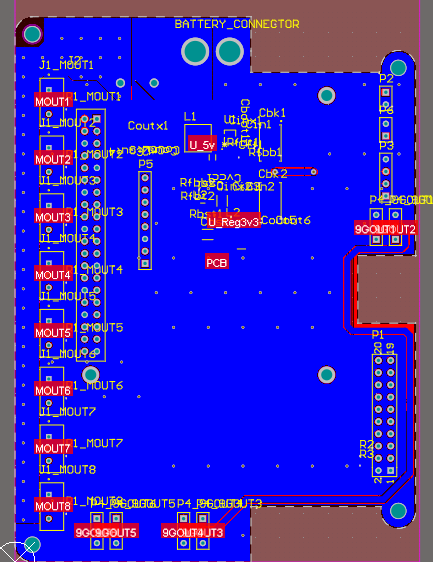

- Arquivo botton_2d.png botton_2d.png adicionado

- Arquivo botton_3d.png botton_3d.png adicionado

- Arquivo top_2d.png top_2d.png adicionado

- Arquivo top_3d.png top_3d.png adicionado

- Arquivo top_3d_com_rasp.png top_3d_com_rasp.png adicionado

Botton layer 2d:

Botton layer 3d:

Top layer 2d:

Top layer 3d sem rasp:

Top layer 3d com rasp:

Atualizado por Gabriel Lima há mais de 5 anos

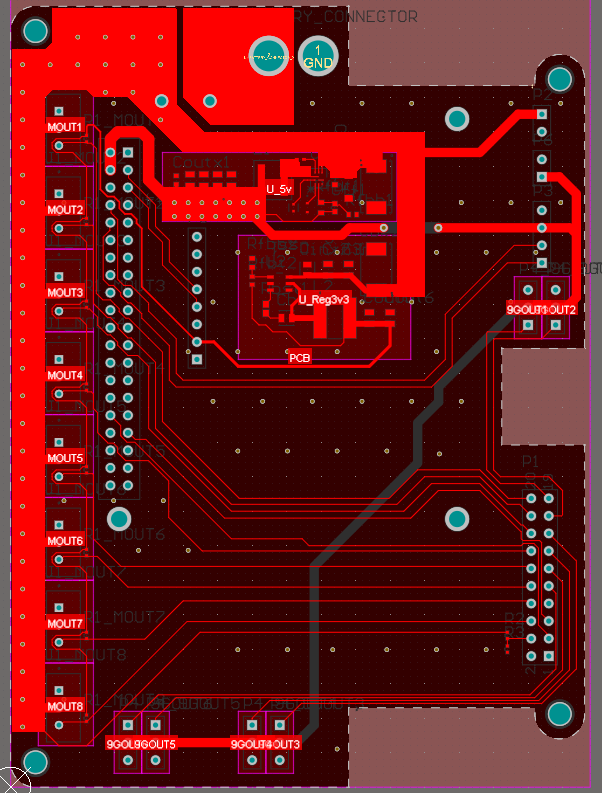

Adicionei uma trilha de alimentasção 5v do Raspberry Pi no bottom layer e mudei de lugar a trilha de alimentação dos servos 3 a 6

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Coloca o print da placa em 2d (bottom e top) dando shelve no plano GND com as alterações

Atualizado por Gabriel Lima há mais de 5 anos

- Arquivo Top_2020-10-15.png Top_2020-10-15.png adicionado

- Arquivo Bottom_2020-10-15.png Bottom_2020-10-15.png adicionado

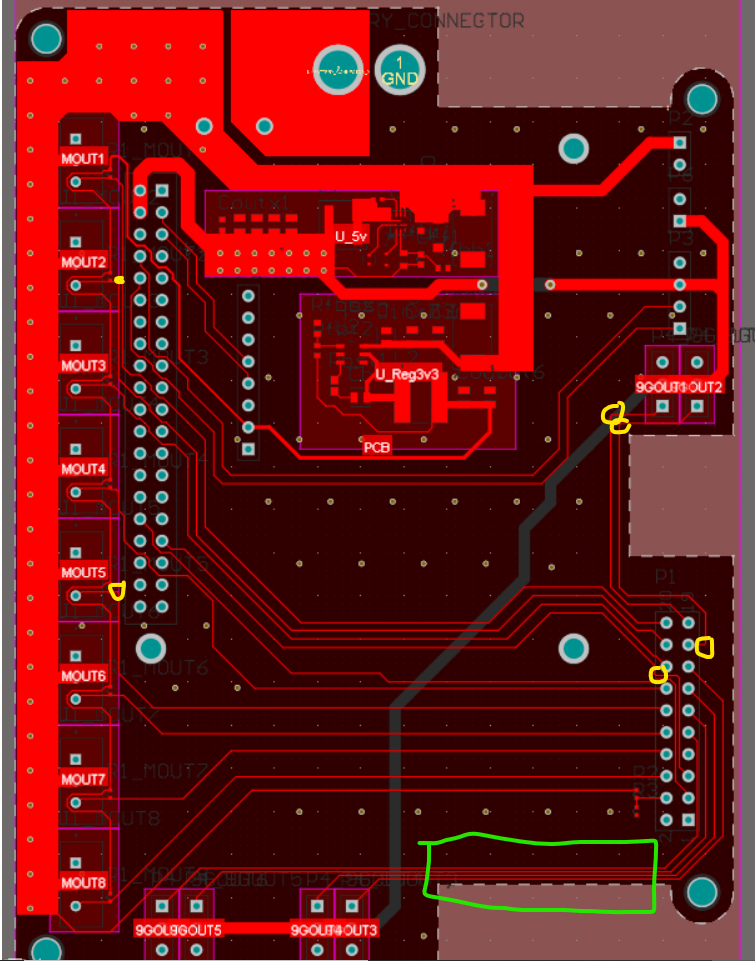

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

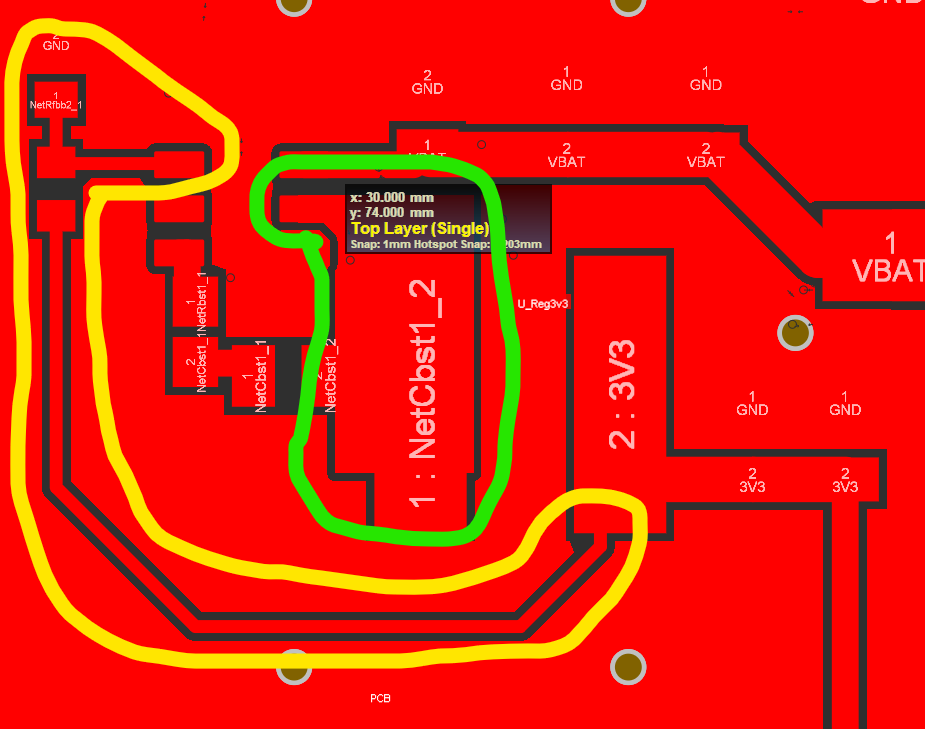

- Arquivo picture622-1.png picture622-1.png adicionado

Elimina essas quinas que eu marquei em amarelo e faz curvas mais suaves. Verifica se há outras quinas no layout.

Em verde, marquei umas trilhas que podem ser mais afastadas da borda da placa porque tem bastante espaço para mexer.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

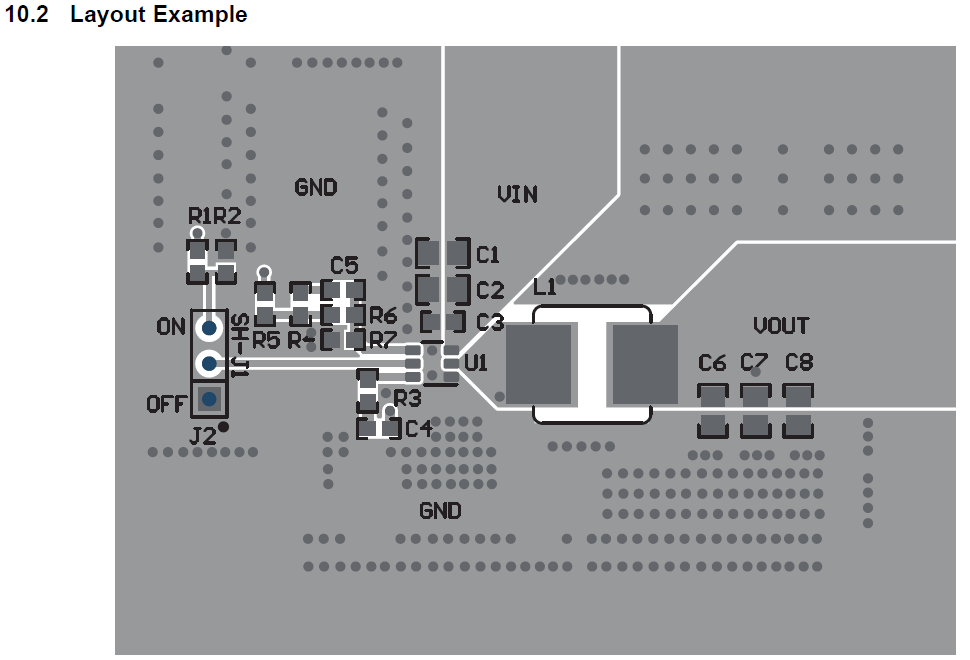

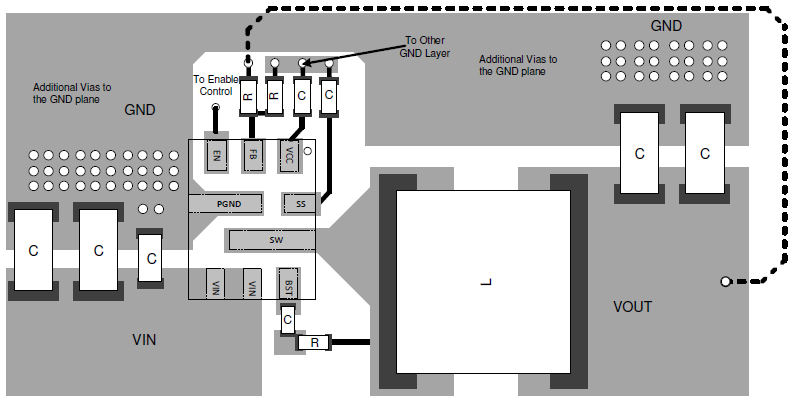

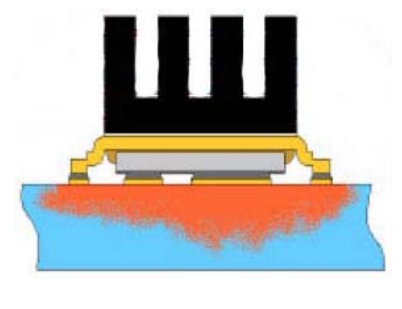

- Arquivo picture61-1.png picture61-1.png adicionado

- Arquivo picture61-2.png picture61-2.png adicionado

Leiam os guidelines no datasheet caso não tenham feito ainda e verifiquem se o layout de vocês está condizente. Estou sem a licença do Altium no meu notebook.

Vou colocar exemplos dos guidelines dos dois circuitos do step down.

3.3V¶

Abaixo está um exemplo do step down 3.3V. O layout de vocês não precisa estar igual a esse para funcionar, mas é importante que vocês leiam os guidelines da seção 10.1 do datasheet do TPS56339

5V¶

Abaixo está um exemplo do circuito de 5V. Esse exemplo foi feito pensando em uma placa de 4 layers, o que torna ainda mais importante ler e verificar o guideline da seção 10.1, agora, do datasheet do TPS56231. Não vai dar para se basear 100% nesse.

Estou sem a licença aqui e não estou conseguindo abrir e visualizar os arquivos para conferir o posicionamento dos componentes

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Coloquem em discussão o MOSFET que vocês estavam querendo usar aqui no redmine também

Atualizado por Gabriel Lima há mais de 5 anos

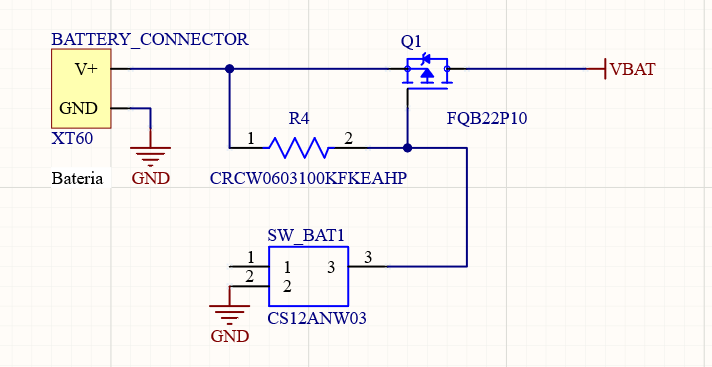

O MOSFET que estamos pensando em utilizar é o FQB22P10 (https://br.mouser.com/datasheet/2/308/FQB22P10-D-1809749.pdf). É um MOSFET P-Channel que suporta nossas necessidades de Ids e Vgs. A ideia é montar um circuito de power no mesmo esquema da VSS, onde uma pequena chave é utilziada apenas para acionar o gate do MOSFET.

Atualizado por Gabriel Lima há mais de 5 anos

Estou fazendo aqui as adequações dos reguladores de tensão aos guidelines do TPS56339 e não entendi o significado dessas três regras e como elas se aplicam ao projeto.

8. Make a Kelvin connection to the GND pin for the feedback path.

9. Voltage feedback loop should be placed away from the high-voltage switching trace, and preferably has

ground shield.

10. The trace of the VFB node should be as small as possible to avoid noise coupling.

Atualizado por Gabriel Lima há mais de 5 anos

Removi as quinas das trilhas e fiz alterações para seguir os guidelines dos reguladores. Só faltam os guidelines do comentário anterior mesmo

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Gabriel Lima escreveu:

Estou fazendo aqui as adequações dos reguladores de tensão aos guidelines do TPS56339 e não entendi o significado dessas três regras e como elas se aplicam ao projeto.

8. Make a Kelvin connection to the GND pin for the feedback path.

9. Voltage feedback loop should be placed away from the high-voltage switching trace, and preferably has

ground shield.

10. The trace of the VFB node should be as small as possible to avoid noise coupling.

VFB seria o nó do pino FB do CI. Pesquisa sobre "buck converter loop" no youtube/google. Daí vai dar para entender bem o que é feedback path, high voltage switching etc..

Atualizado por Gabriel Lima há mais de 5 anos

- Arquivo Reg_3v3_2020-10-16.png Reg_3v3_2020-10-16.png adicionado

Pesquisamos aqui e ainda não entendemos como o Kelvin Connection seria aplicado no nosso caso. O 9 e o 10 foram feitos na medida do possível.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

Talvez não seja aplicável nesse design. A conexão seria feita em torno do resistor R6. No caso do layout do datasheet que eu enviei acima, ela seria o resistor R4 em série com o C5.

No caso, não vi outras citações sobre como dimensionar eles no datasheet - diferente dos outros componentes do design. Na verdade, só vi eles sendo mencionados durante os guidelines.

Atualizado por André Vidal há mais de 5 anos

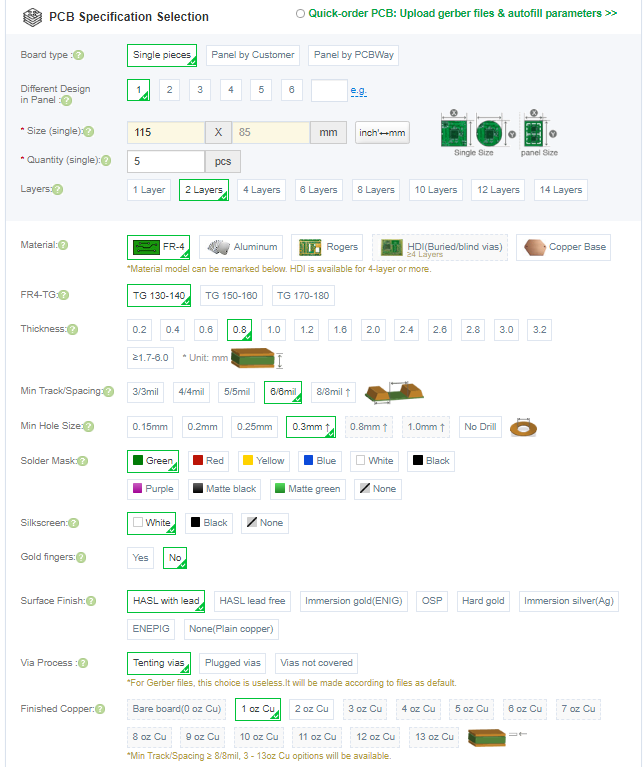

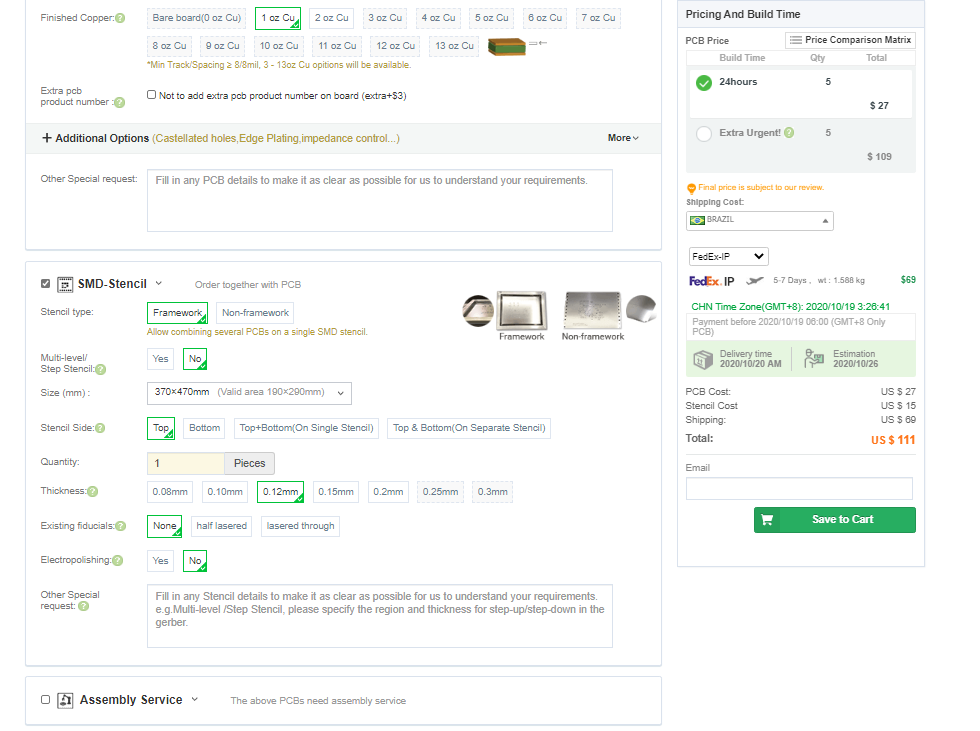

O preço pelo PCBWay, usando FedEx ficou o seguinte:

PCB Cost: US$ 27

Stencil Cost: US$ 15

Shipping: US$ 69

-----------------------------

Total: US$ 111

Atualizado por André Vidal há mais de 5 anos

Montado o esquemático do circuito de Power.

Atualizado por André Vidal há mais de 5 anos

- Arquivo Power_2020-10-18.png Power_2020-10-18.png adicionado

Atualizado por Gabriel Lima há mais de 5 anos

Terminamos de colocar o circuito de power na PCB e novamente temos um projeto sem erros elétricos na compilação.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

André Vidal escreveu:

O preço pelo PCBWay, usando FedEx ficou o seguinte:

PCB Cost: US$ 27

Stencil Cost: US$ 15

Shipping: US$ 69

-----------------------------

Total: US$ 111

Manda um print dos parâmetros de manufatura que vocês colocaram lá.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

André Vidal escreveu:

Verificaram a potência dissiada no MOSFET para ver se precisa do dissipador? Coloca as contas aqui

Atualizado por André Vidal há mais de 5 anos

- Arquivo parametros_compra_1_2020-10-18.png parametros_compra_1_2020-10-18.png adicionado

- Arquivo parametros_compra_2_2020-10-18.png parametros_compra_2_2020-10-18.png adicionado

Erick Bezerra de Carvalho escreveu:

André Vidal escreveu:

O preço pelo PCBWay, usando FedEx ficou o seguinte:

PCB Cost: US$ 27

Stencil Cost: US$ 15

Shipping: US$ 69

-----------------------------

Total: US$ 111Manda um print dos parâmetros de manufatura que vocês colocaram lá.

Seguem os parâmetros:

Atualizado por André Vidal há mais de 5 anos

- Arquivo PowerNovo_2020-10-18.png PowerNovo_2020-10-18.png adicionado

Erick Bezerra de Carvalho escreveu:

André Vidal escreveu:

Verificaram a potência dissiada no MOSFET para ver se precisa do dissipador? Coloca as contas aqui

Foram feitas as contas e foi visto que a resistência do MOSFET era muito grande. Então ele foi substituído pelo IRF9383 (https://br.mouser.com/datasheet/2/196/irf9383mpbf-1732502.pdf).

Segue abaixo como ficou.

Atualizado por Gabriel Lima há mais de 5 anos

- Arquivo Dissipador_IRF9383.png Dissipador_IRF9383.png adicionado

Fizemos aqui os cálculos de dissipação de potência no MOSFET. A resistência Drain-Source quando acionado com tensão de 10V no gate é de 2.9mOhms. Assim, para a corrente de pico de 22A, será dissipada uma potência de 1.4W, menor que a limite de 2.1W. Caso necessário, também dá para colocar um dissipador de calor colado sobre o MOSFET.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

André Vidal escreveu:

Erick Bezerra de Carvalho escreveu:

André Vidal escreveu:

O preço pelo PCBWay, usando FedEx ficou o seguinte:

PCB Cost: US$ 27

Stencil Cost: US$ 15

Shipping: US$ 69

-----------------------------

Total: US$ 111Manda um print dos parâmetros de manufatura que vocês colocaram lá.

Seguem os parâmetros:

A grossura padrão é 1,6mm. Vê quanto fica o preço para 10 placas também. Da última vez que eu pedi, o preço para pedir 5 e 10 era o mesmo.

Lembra de demarcar as bordas da placa antes também. A marcação pode ser feita na Mechanical Layer 1 mesmo, mas confere se não tem nenhuma outra coisa nessa layer.

Tirando isso, se eu não me engano, tem um tutorial no próprio site da PCBWay também que ensina a gerar os gerbers necessários para envio. Na prática, devem ser gerados os gerbers e os arquivos de furação para o envio.

Atualizado por André Vidal há mais de 5 anos

Foi modificado o projeto da placa para as limitações do LPKF, sendo criada uma nova branch (LPKF). Adcionamos também o conector do LIDAR VL53L0X.

Existe alguma tolerância para a Clearance Constraint de 0.2mm? No regulador de 5v há casos de 0.195mm na distância entre os pads. Os stitchs foram retirados e posteriormente serão recolocados.

Atualizado por Erick Bezerra de Carvalho há mais de 5 anos

André Vidal escreveu:

Foi modificado o projeto da placa para as limitações do LPKF, sendo criada uma nova branch (LPKF). Adcionamos também o conector do LIDAR VL53L0X.

Existe alguma tolerância para a Clearance Constraint de 0.2mm? No regulador de 5v há casos de 0.195mm na distância entre os pads. Os stitchs foram retirados e posteriormente serão recolocados.

Tem que verificar com o local que vai fazer a manufatura. No pior dos casos, dá para substituir o step down de 5v pelo de 3.3V mudando um pouco o circuito dele

Atualizado por Gabriel Lima há mais de 5 anos

Foram trocados os componentes pelos equivalentes que tinha na IMBEL de acordo com a lista que o Sérgio colocou na planilha do BOM

Atualizado por André Vidal há mais de 5 anos

O projeto sofreu trocas de componentes em virtude dos novos estarem disponíveis da IMBEL, havendo mudanças na PCB. Foi prototipada a primeira placa. Porém, com as mudanças nos componentes, ela irá sofrer alterações, também por conta dos conectores dos motores AX12 precisarem de um diâmetro maior nos furos dos pinos que não são GND.

Atualizado por Gabriel Lima há quase 5 anos

- Situação alterado de Em andamento para Fechada